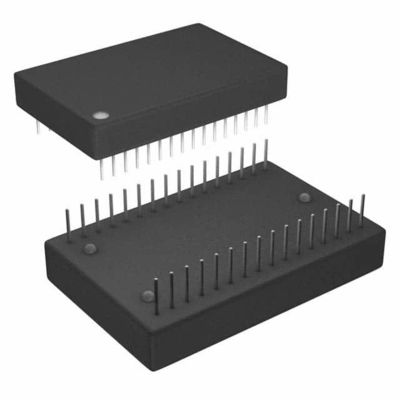

28EDIP Practical Clock And Timing IC , DS1286 Realtime Clock IC

| Features | Alarm, Leap Year, Square Wave Output, SRAM, Watchdog Timer | Type | Clock/Calendar |

|---|---|---|---|

| Memory Size | 50B | Time Format | HH:MM:SS:hh (12/24 Hr) |

| Date Format | YY-MM-DD-dd | Interface | Parallel |

| Voltage - Supply | 4.5V ~ 5.5V | Voltage - Supply, Battery | 2.4V ~ 3.5V |

| Current - Timekeeping (Max) | 7mA @ 5V | Operating Temperature | 0°C ~ 70°C |

| Mounting Type | Through Hole | Package / Case | 28-DIP Module (0.61", 15.49mm), 23 Leads |

| Supplier Device Package | 28-EDIP | ||

| Highlight | 28EDIP Clock And Timing IC,Practical Clock And Timing IC,DS1286 Realtime Clock IC |

||

DS1286 IC RTC CLK/CALENDAR PAR 28EDIP Analog Devices Inc./Maxim Integrated

Product Details

GENERAL DESCRIPTION

The DS1284/DS1286 watchdog timekeepers are self-contained real-time clocks, alarms, watchdog timers, and interval timers in a 28-pin JEDEC DIP and encapsulated DIP package. The DS1286 contains an embedded lithium energy source and a quartz crystal, which eliminates the need for any external circuitry. The DS1284 requires an external quartz crystal and a VBAT source, which could be a lithium battery. Data contained within 64 8-bit registers can be read or written in the same manner as byte-wide static RAM. Data is maintained in the watchdog timekeeper by intelligent control circuitry that detects the status of VCC and write protects memory when VCC is out of tolerance. The lithium

FEATURES

Keeps Track of Hundredths of Seconds, Seconds, Minutes, Hours, Days, Date of the Month, Months, and Years; Valid Leap Year Compensation Up to 2100 Watchdog Timer Restarts an Out-of-Control Processor

Alarm Function Schedules Real-Time-Related Activities

Embedded Lithium Energy Cell Maintains Time, Watchdog, User RAM, and Alarm Information

Programmable Interrupts and Square-Wave Outputs Maintain JEDEC Footprint

All Registers are Individually Addressable via the Address and Data Bus

Accuracy is Better than ±1 Minute/Month at +25°C (EDIP)

Greater than 10 Years of Timekeeping in the Absence of VCC

50 Bytes of User NV RAM

Underwriters Laboratory (UL) Recognized

-40°C to +85°C Industrial Temperature Range Option

Specifications

| Attribute | Attribute Value |

|---|---|

| Manufacturer | Maxim Integrated |

| Product Category | IC Chips |

| Series | - |

| Type | Clock/Calendar |

| Packaging | Tube |

| Package-Case | 28-DIP Module (0.61", 15.49mm) 23 leads |

| Operating-Temperature | 0°C ~ 70°C |

| Mounting-Type | Through Hole |

| Features | Alarm, Leap Year, Square Wave Output, SRAM, Watchdog Timer |

| Interface | Parallel |

| Voltage-Supply | 4.5 V ~ 5.5 V |

| Supplier-Device-Package | 28-EDIP |

| Memory Capacity | 50B |

| Time-Format | HH:MM:SS:hh (12/24 hr) |

| Date-Format | YY-MM-DD-dd |

| Voltage-Supply-Battery | 2.4 V ~ 3.5 V |

| Current-Timekeeping-Max | 7mA @ 5V |

Features, Applications

FEATURES

Keeps track of hundredths of seconds, minutes, hours, days, date of the month, months, and years; valid leap year compensation to 2100 Watchdog timer restarts an out-of-control processor Alarm function schedules real time-related activities Embedded lithium energy cell maintains time, watchdog, user RAM, and alarm information Programmable interrupts and square wave outputs maintain 28-pin JEDEC footprint All registers are individually addressable via the address and data bus Accuracy is better than ±1 minute/month at 25°C Greater than 10 years of timekeeping in the absence of VCC 50 bytes of user NV RAM

- Interrupt Output A (open drain) INTB (INTB) - Interrupt Output B (open drain) A0-A5 - Address Inputs DQ0-DQ7 - Data Input/Output CE - Chip Enable OE - Output Enable WE - Write Enable VCC - +5 Volts GND - Ground - No Connection SQW - Square Wave Output

DESCRIPTION

The DS1286 Watchdog Timekeeper is a self-contained real time clock, alarm, watchdog timer, and interval timer a 28-pin JEDEC DIP package. The DS1286 contains an embedded lithium energy source and a quartz crystal which eliminates the need for any external circuitry. Data contained within 64 eightbit registers can be read or written in the same manner as bytewide static RAM. Data is maintained in the Watchdog Timekeeper by intelligent control circuitry which detects the status of VCC and write protects memory when VCC is out of tolerance. The lithium energy source can maintain data and real time for over 10 years in the absence of VCC. Watchdog Timekeeper information includes hundredths of seconds, minutes, hours, day, date, month, and year. The date at the end of the month is automatically 13 111999

adjusted for months with less than 31 days, including correction for leap year. The Watchdog Timekeeper operates in either or 12-hour format with an AM/PM indicator. The watchdog timer provides alarm windows and interval timing between 0.01 seconds and 99.99 seconds. The real time alarm provides for preset times up to one week.

The DS1286 executes a read cycle whenever WE (Write Enable) is inactive (High) and CE (Chip Enable) and OE (Output Enable) are active (Low). The unique address specified by the six address inputs (A0-A5) defines which of the 64 registers to be accessed. Valid data will be available to the eight data output drivers within tACC (Access Time) after the last address input signal is stable, providing that CE and OE access times are also satisfied. If OE and CE access times are not satisfied, then data access must be measured from the latter occurring signal OE ) and the limiting parameter is either tCO for CE or tOE for OE rather than address access.

The is in the write mode whenever the WE (Write Enable) and CE (Chip Enable) signals are in the active (Low) state after the address inputs are stable. The latter occurring falling edge or WE will determine the start of the write cycle. The write cycle is terminated by the earlier rising edge CE or WE. All address inputs must be kept valid throughout the write cycle. WE must return to the high state for a minimum recovery state (tWR) before another cycle can be initiated. Data must be valid on the data bus with sufficient Data Set Up (tDS) and Data Hold Time (tDH) with respect to the earlier rising edge CE or WE. The OE control signal should be kept inactive (High) during write cycles to avoid bus contention. However, if the output bus has been enabled ( CE and OE active), then WE will disable the outputs in tODW from its falling edge.

The Watchdog Timekeeper provides full functional capability when VCC is greater than 4.5 volts and write protects the register contents at 4.25 volts typical. Data is maintained in the absence of VCC without any additional support circuitry. The DS1286 constantly monitors VCC. Should the supply voltage decay, the Watchdog Timekeeper will automatically write protect itself and all inputs to the registers become "Don't Care." Both INTA and INTB (INTB) are open drain outputs. The two interrupts and the internal clock continue to run regardless of the level of VCC. However, it is important to insure that the pull-up resistors used with the interrupt pins are never pulled to a value which is greater than VCC 0.3V. As VCC falls below approximately 3.0 volts, a power switching circuit turns on the lithium energy source to maintain the clock, and timer data functionality. It is also required to insure that during this time (battery backup mode), the voltage present at INTA and INTB (INTB) never exceeds 3.0V. At all times the current on each should not exceed or -1.0 mA. However, if the active high mode is selected for INTB (INTB), this pin will only go high in the presence of VCC. During power-up, when VCC rises above approximately 3.0 volts, the power switching circuit connects external VCC and disconnects the internal lithium energy source. Normal operation can resume after VCC exceeds 4.5 volts for a period of 150 ms.

The Watchdog Timekeeper has 64 registers which are 8 bits wide that contain all of the Timekeeping, Alarm, Watchdog, Control, and Data information. The Clock, Calendar, Alarm, and Watchdog registers are memory locations which contain external (user-accessible) and internal copies of the data. The external copies are independent of internal functions except that they are updated periodically by the simultaneous transfer of the incremented internal copy (see Figure 1). The Command Register bits are affected by both internal and external functions. This register will be discussed later. The 50 bytes of RAM registers can only be accessed from the external address and data bus. Registers and A contain time of day and date information (see Figure 2). Time of Day information is stored in BCD. Registers 3, 5, and 7 contain the Time of Day Alarm information. Time of Day Alarm information is stored in BCD. Register B is the Command Register and information in this register is binary. Registers C and D are the Watchdog Alarm registers and information which is stored in these two registers is in BCD. Registers E through 3F are user bytes and can be used to contain data at the user's discretion.